# LCD Segment / Common Driver With Controller CMOS

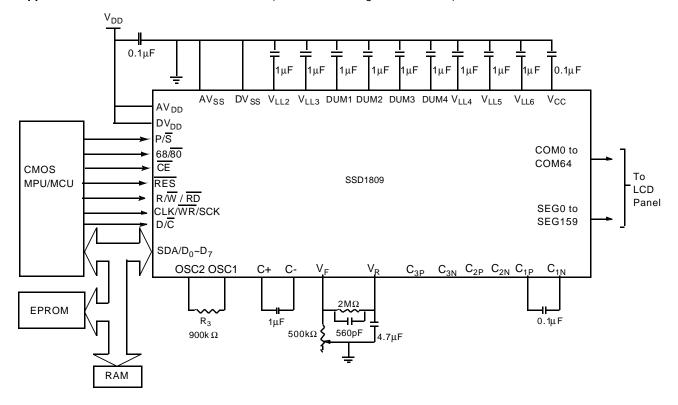

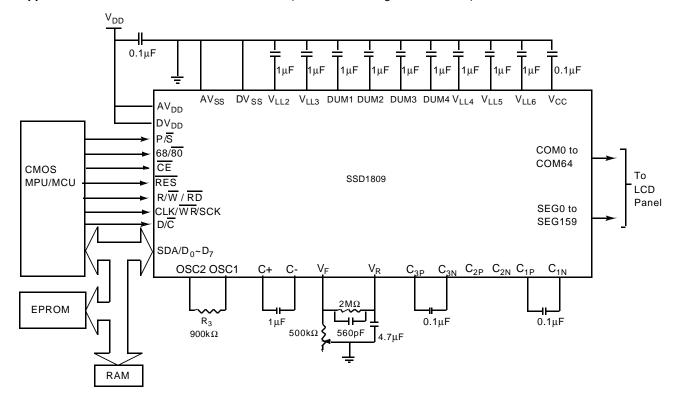

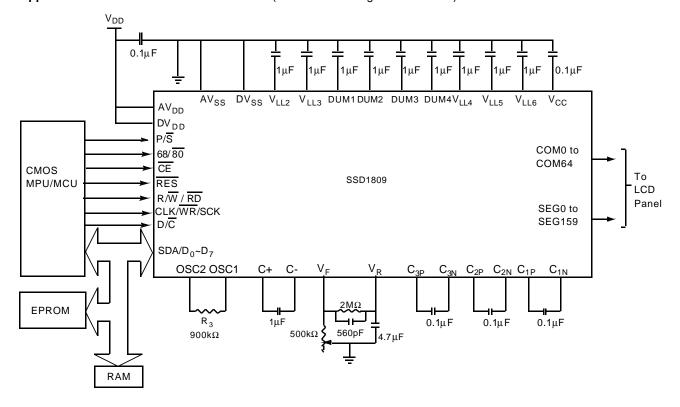

SSD1809 is a single-chip CMOS LCD driver with controller for liquid crystal dot-matrix graphic display system. It consists of 225 high voltage driving output pins for driving 160 Segments, 64 Commons and 1icon driving-Common.

SSD1809 displays data directly from its internal Graphic RAM (160x65). Data/Commands are sent from general MCU through a software selectable 6800-/8080-series compatible Parallel Interface or Serial Peripheral Interface.

SSD1809 embeds a DC-DC Converter, an On-chip Bias Divider and an On-Chip Oscillator which reduce the number of external components. With the special design on minimizing power consumption and package layout, SSD1809 is suitable for any portable battery-driven application requiring a long operation period and a compact size.

- 160x64 Graphic Display with a Icon Line

- Programmable Multiplex Ratio (1 Mux 65 Mux) [Partial Display]

- Graphic Display Mode Operation / Chinese Character Display Mode Operation

- Supply Operation, 2.2 V 3.5 V

- Enhanced Low Power Icon Mode (160 icons, <19uA)

- On-Chip Internal DC-DC Converter / External Power Supply

- 2X / 3X / 4X / 5X DC-DC Converter

- On-Chip Oscillator

- On-Chip Bias Voltage Generator

- 1:5 / 1:7 / 1:8 / 1:9 Bias Ratio

- Maximum 16.5V LCD Driving Output Voltage

- 8-bit 6800-Series Parallel Interface, 8-bit 80-Series Parallel Interface and Serial Peripheral Interface (SPI)

- On-Chip 160 x 65 Display Data RAM

- · Re-mapping of Row and Column Drivers

- Vertical Scrolling

- · Display Masks for implementation of blinking effect

- Programmable Frame Frequency

- Master Clear RAM

- External Contrast Control

- 16 Level Internal Contrast Control

- Selectable LCD Driving Voltage Temperature Coefficients

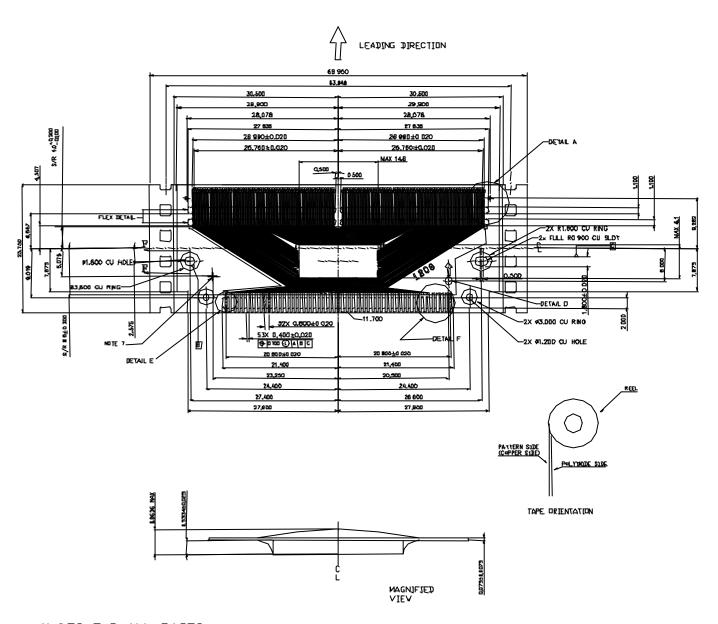

- Available in TAB (Tape Automated Bonding)

SSD1809

This document contains information on a new product. Specifications and information herein and subject to change without notice.

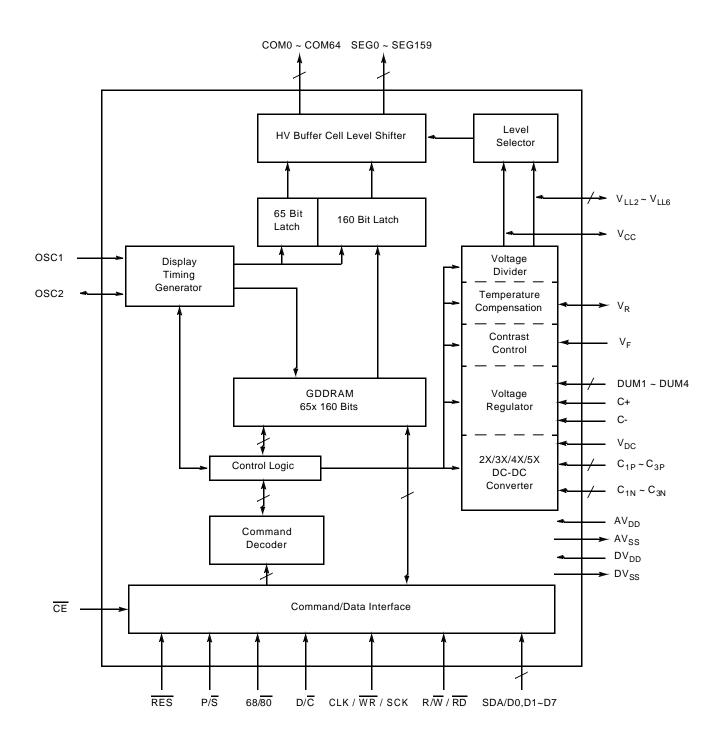

# **Block Diagram**

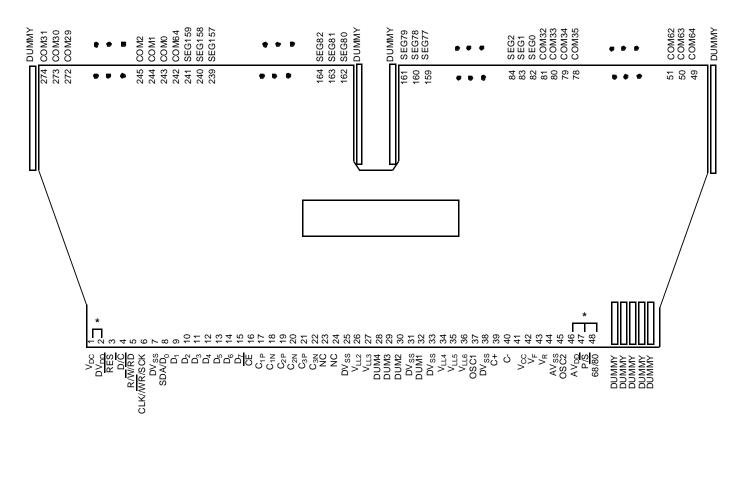

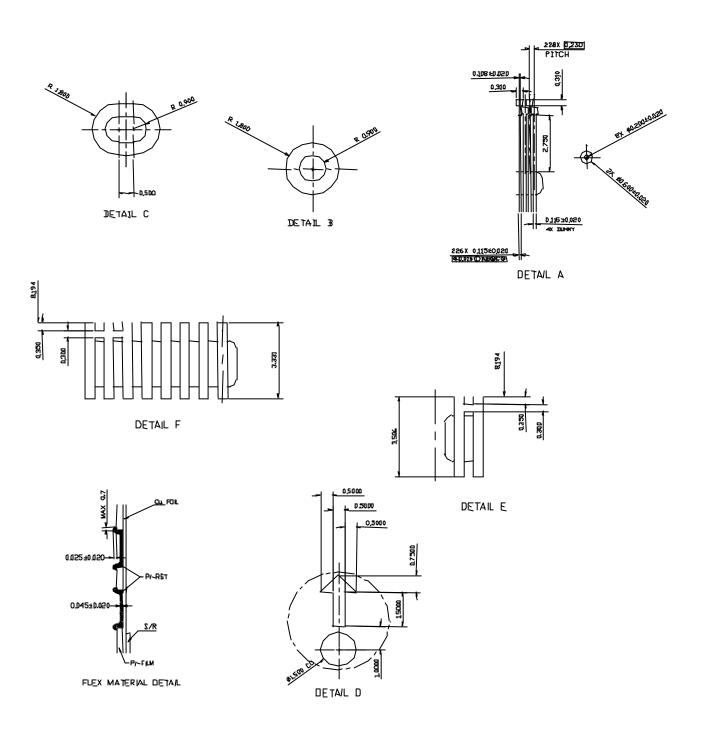

# **SSD1809T PIN ASSIGNMENT**

(COPPER VIEW)

**Normal Design TAB**

\*Remarks: In the TAB package, pin1(VDC) & pin2(DVDD) are connected to DVDD. Pin46(AVDD), pin47(P/S) & pin48(68/80) are connected to AVDD.

REV 1.3 03/02 **SOLOMON** SSD1809

# SSD1809T Pin Assignment Table

| TAB<br>Pin#    | Signal Name              | TAB<br>Pin# | Signal Name    | TAB<br>Pin # | Signal Name             | TAB<br>Pin #      | Signal Name                | TAB<br>Pin # | Signal Name |

|----------------|--------------------------|-------------|----------------|--------------|-------------------------|-------------------|----------------------------|--------------|-------------|

| 1              | $V_{DC}$                 | 61          | COM52          | 121          | SEG39                   | 181               | SEG99                      | 241          | SEG159      |

| 2              | DVDD                     | 62          | COM51          | 122          | SEG40                   | 182               | SEG100                     | 242          | COM64       |

| 3              | RES                      | 63          | COM50          | 123          | SEG41                   | 183               | SEG101                     | 243          | COM0        |

| 4              | D/C                      | 64          | COM49          | 124          | SEG42                   | 184               | SEG102                     | 244          | COM1        |

|                |                          |             |                |              |                         |                   |                            |              |             |

| 5              | R/W / RD                 | 65          | COM48          | 125          | SEG43                   | 185               | SEG103                     | 245          | COM2        |

| 6              | CLK/WR/SCK               | 66          | COM47          | 126          | SEG44                   | 186               | SEG104                     | 246          | COM3        |

| 7              | DV <sub>SS</sub>         | 67          | COM46          | 127          | SEG45                   | 187               | SEG105                     | 247          | COM4        |

| 8              | SDA/D <sub>0</sub>       | 68          | COM45          | 128          | SEG46                   | 188               | SEG106                     | 248          | COM5        |

| 9              |                          | 69          | COM44          | 129          | SEG47                   | 189               | SEG107                     | 249          | COM6        |

|                | $D_1$                    |             |                |              |                         |                   |                            |              |             |

| 10             | $D_2$                    | 70          | COM43          | 130          | SEG48                   | 190               | SEG108                     | 250          | COM7        |

| 11             | $D_3$                    | 71          | COM42          | 131          | SEG49                   | 191               | SEG109                     | 251          | COM8        |

| 12             | $D_4$                    | 72          | COM41          | 132          | SEG50                   | 192               | SEG110                     | 252          | COM9        |

| 13             | D <sub>5</sub>           | 73          | COM40          | 133          | SEG51                   | 193               | SEG111                     | 253          | COM10       |

| 14             | $D_6^{\circ}$            | 74          | COM39          | 134          | SEG52                   | 194               | SEG112                     | 254          | COM11       |

| 15             | D 6                      | 75          | COM38          | 135          | SEG53                   | 195               | SEG113                     | 255          | COM12       |

|                | D <sub>7</sub><br>CE     |             |                |              |                         |                   |                            |              |             |

| 16             |                          | 76          | COM37          | 136          | SEG54                   | 196               | SEG114                     | 256          | COM13       |

| 17             | C <sub>1P</sub>          | 77          | COM36          | 137          | SEG55                   | 197               | SEG115                     | 257          | COM14       |

| 18             | C <sub>1N</sub>          | 78          | COM35          | 138          | SEG56                   | 198               | SEG116                     | 258          | COM15       |

| 19             | C <sub>2P</sub>          | 79          | COM34          | 139          | SEG57                   | 199               | SEG117                     | 259          | COM16       |

| 20             | C <sub>2N</sub>          | 80          | COM33          | 140          | SEG58                   | 200               | SEG118                     | 260          | COM17       |

| 21             |                          | 81          | COM32          | 141          | SEG59                   | 201               | SEG119                     | 261          | COM18       |

| 22             | C <sub>3P</sub>          | 82          | SEG0           | 141          |                         | 201               | SEG119<br>SEG120           | 262          | COM18       |

|                | C <sub>3N</sub><br>NC    |             |                |              | SEG60                   |                   |                            |              |             |

| 23             |                          | 83          | SEG1           | 143          | SEG61                   | 203               | SEG121                     | 263          | COM20       |

| 24             | NC                       | 84          | SEG2           | 144          | SEG62                   | 204               | SEG122                     | 264          | COM21       |

| 25             | DV <sub>SS</sub>         | 85          | SEG3           | 145          | SEG63                   | 205               | SEG123                     | 265          | COM22       |

| 26             | $V_{LL2}$                | 86          | SEG4           | 146          | SEG64                   | 206               | SEG124                     | 266          | COM23       |

|                | VLL2                     |             | SEG5           |              |                         |                   |                            |              |             |

| 27             | $V_{LL3}$                | 87          |                | 147          | SEG65                   | 207               | SEG125                     | 267          | COM24       |

| 28             | DÜM4                     | 88          | SEG6           | 148          | SEG66                   | 208               | SEG126                     | 268          | COM25       |

| 29             | DUM3                     | 89          | SEG7           | 149          | SEG67                   | 209               | SEG127                     | 269          | COM26       |

| 30             | DUM2                     | 90          | SEG8           | 150          | SEG68                   | 210               | SEG128                     | 270          | COM27       |

| 31             | DV <sub>SS</sub>         | 91          | SEG9           | 151          | SEG69                   | 211               | SEG129                     | 271          | COM28       |

| 32             | DUM1                     | 92          | SEG10          | 152          | SEG70                   | 212               | SEG130                     | 272          | COM29       |

|                |                          |             |                |              |                         |                   |                            |              |             |

| 33             | DV <sub>SS</sub>         | 93          | SEG11          | 153          | SEG71                   | 213               | SEG131                     | 273          | COM30       |

| 34             | $V_{LL4}$                | 94          | SEG12          | 154          | SEG72                   | 214               | SEG132                     | 274          | COM31       |

| 35             | V <sub>LL5</sub>         | 95          | SEG13          | 155          | SEG73                   | 215               | SEG133                     |              |             |

| 36             | VILE                     | 96          | SEG14          | 156          | SEG74                   | 216               | SEG134                     |              |             |

| 37             | V <sub>LL6</sub><br>OSC1 | 97          | SEG15          | 157          | SEG75                   | 217               | SEG135                     |              |             |

|                |                          |             |                |              |                         |                   |                            |              |             |

| 38             | DV <sub>SS</sub>         | 98          | SEG16          | 158          | SEG76                   | 218               | SEG136                     |              |             |

| 39             | C+                       | 99          | SEG17          | 159          | SEG77                   | 219               | SEG137                     |              |             |

| 40             | C-                       | 100         | SEG18          | 160          | SEG78                   | 220               | SEG138                     |              |             |

| 41             | V <sub>cc</sub>          | 101         | SEG19          | 161          | SEG79                   | 221               | SEG139                     |              |             |

| 42             | V <sub>F</sub>           | 102         | SEG20          | 162          | SEG80                   | 222               | SEG140                     |              |             |

| 43             | V <sub>R</sub>           | 103         | SEG21          | 163          | SEG81                   | 223               | SEG141                     |              |             |

|                | AV/                      |             | SEG21<br>SEG22 |              |                         |                   |                            |              | 1           |

| 44             | AVSS                     | 104         |                | 164          | SEG82                   | 224               | SEG142                     |              |             |

| 45             | AV <sub>SS</sub><br>OSC2 | 105         | SEG23          | 165          | SEG83                   | 225               | SEG143                     |              | 1           |

| 46             | AV <sub>DD</sub>         | 106         | SEG24          | 166          | SEG84                   | 226               | SEG144                     |              | 1           |

| 47             | P/S                      | 107         | SEG25          | 167          | SEG85                   | 227               | SEG145                     |              | 1           |

| 48             | 68/80                    | 108         | SEG26          | 168          | SEG86                   | 228               | SEG146                     |              | 1           |

|                |                          |             |                |              |                         |                   |                            |              | 1           |

| 49<br>50       | COM64<br>COM63           | 109<br>110  | SEG27<br>SEG28 | 169<br>170   | SEG87<br>SEG88          | 229<br>230        | SEG147<br>SEG148           |              |             |

|                |                          |             |                |              |                         |                   |                            |              |             |

| 51             | COM62                    | 111         | SEG29          | 171          | SEG89                   | 231               | SEG149                     |              |             |

| 52             | COM61                    | 112         | SEG30          | 172          | SEG90                   | 232               | SEG150                     |              | 1           |

| 53             | COM60                    | 113         | SEG31          | 173          | SEG91                   | 233               | SEG151                     |              | 1           |

| 54             | COM59                    | 114         | SEG32          | 174          | SEG92                   | 234               | SEG152                     |              | 1           |

| <b>○</b> .     | COM58                    | 115         | SEG33          | 175          | SEG93                   | 235               | SEG153                     |              | 1           |

| 55             |                          |             |                |              |                         |                   |                            |              | 1           |

| 55             | COM57                    | 116         | SEG34          | 176          | SEG94                   | 236               | SEG154                     |              |             |

| 56             |                          | 447         | SEG35          | 177          | SEG95                   | 237               | SEG155                     |              | Ī           |

|                | COM56                    | 117         | OLOGO          |              |                         |                   |                            |              |             |

| 56             | COM56<br>COM55           | 117         | SEG36          | 178          | SEG96                   | 238               | SEG156                     |              |             |

| 56<br>57<br>58 | COM55                    | 118         | SEG36          | 178          |                         |                   |                            |              |             |

| 56<br>57       |                          |             |                |              | SEG96<br>SEG97<br>SEG98 | 238<br>239<br>240 | SEG156<br>SEG157<br>SEG158 |              |             |

# **MAXIMUM RATINGS\*** (Voltages Referenced to $V_{SS}$ , $T_A$ =25° C)

| Symbol                   | Parameter                                             | Value                          | Unit |

|--------------------------|-------------------------------------------------------|--------------------------------|------|

| $AV_{DD},DV_{DD},V_{DC}$ | Supply Voltage                                        | -0.3 to +4.0                   | V    |

| V <sub>CC</sub>          |                                                       | $V_{SS}$ -0.3 to $V_{SS}$ +18  | V    |

| V <sub>in</sub>          | Input Voltage                                         | $V_{SS}$ -0.3 to $V_{DD}$ +0.3 | V    |

| I                        | Current Drain Per Pin Excluding $V_{DD}$ and $V_{SS}$ | 25                             | mA   |

| T <sub>A</sub>           | Operating Temperature                                 | -30 to +85                     | °C   |

| T <sub>stg</sub>         | Storage Temperature Range                             | -65 to +150                    | °C   |

<sup>\*</sup> Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Electrical Characteristics tables or Pin Descrip-

$\rm V_{SS} = AV_{SS} = DV_{SS} \, (DV_{SS} = V_{SS} \, of \, Digital \, \, circuit, \, AV_{SS} = V_{SS} \, of \, Analogue \, Circuit)$  $V_{DD} = AV_{DD} = DV_{DD} \ (DV_{DD} = V_{DD} \ of \ Digital \ circuit, \ AV_{DD} = V_{DD} \ of \ Analogue \ Circuit)$  This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions to be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS}$  < or =  $(V_{in} \text{ or } V_{out})$  < or =  $V_{DD}$ . Reliability of operation is enhanced if unused input are connected to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{DD}$ ). Unused outputs must be left open. This device may be light sensitive. Caution should be taken to avoid exposure of this device to any light source during normal operation. This device is not radiation protected.

# **ELECTRICAL CHARACTERISTICS** (Voltage Referenced to $V_{SS}$ , $V_{DD}$ =2.2 to 3.5V, $T_A$ =25° C; unless otherwise specified.)

| Symbol                               | Parameter                                                                                     | Test Condition                                                                                                                                                                      | Min                 | Тур             | Max                  | Unit   |

|--------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|----------------------|--------|

| DV <sub>DD</sub><br>AV <sub>DD</sub> | Logic Circuit Supply Voltage Range<br>Voltage Generator Circuit Supply Voltage Range          | (Absolute value referenced to V <sub>SS</sub> )                                                                                                                                     | 2.2<br>2.2          | 3.0             | 3.5<br>3.5           | V<br>V |

| V <sub>DC</sub>                      | DC/DC Converter Circuit Supply Voltage Range                                                  |                                                                                                                                                                                     | 2.2                 | -               | 3.5                  | V      |

| I <sub>AC</sub>                      | Access Mode Supply Current Drain (AV <sub>DD</sub> + DV <sub>DD</sub> + V <sub>DC</sub> Pins) | V <sub>DD</sub> =3.0V, Voltage Generator On, 5X Converter Enabled, 65Mux Ratio, R/W accessing, T <sub>cyc</sub> =200kHz, Internal Oscillator Enabled, Frame Freq.=60Hz, Display On. | -                   | -               | 450                  | μА     |

| I <sub>DP</sub>                      | Display Mode Supply Current Drain<br>(AV <sub>DD</sub> + DV <sub>DD</sub> Pins)               | V <sub>DD</sub> =3.0V, Voltage Generator On, 5X Converter<br>Enabled, 65Mux Ratio, R. → Halt, Internal Oscillator<br>Enabled, Frame Freq.=60Hz, Display On.                         | -                   | 170             | 270                  | μΑ     |

| I <sub>SB</sub>                      | Standby Mode Supply Current Drain (AV <sub>DD</sub> + DV <sub>DD</sub> Pins)                  | V <sub>DD</sub> =3.0V, Display Off, Oscillator Disabled, R <sub>W</sub> halt.                                                                                                       | -                   | -               | 1                    | μА     |

| I <sub>ICON</sub>                    | Icon Mode Supply Current Drain<br>(AV <sub>DD</sub> + DV <sub>DD</sub> Pins)                  | V <sub>DD</sub> =3.0V, Internal Oscillator Enabled, 65Mux Ratio,<br>Display On, Icon Mode C, R/W halt, Frame Freq.=<br>81.25Hz                                                      | -                   | 11              | 19                   | μА     |

| V <sub>CC</sub>                      | LCD Driving Voltage Generator Output (V <sub>CC</sub> Pin)                                    | Display On, Voltage Generator Enabled,<br>DC/DC Converter Enabled, Frame Freq.=60Hz,<br>Voltage Regulator Enabled, Voltage Divider Enabled.                                         | 5                   | -               | 16.5                 | V      |

| $V_{LCD}$                            | LCD Driving Voltage Input (V <sub>CC</sub> Pin)                                               | Voltage Generator Disabled, 1:5 Bias.                                                                                                                                               | 5                   | -               | 16.5                 | V      |

| V <sub>OH1</sub>                     | Output High Voltage<br>(SDA/D <sub>0</sub> -D <sub>7</sub> , OSC2)                            | I <sub>out</sub> =100mA                                                                                                                                                             | 0.9*V <sub>DD</sub> | -               | V <sub>DD</sub>      | V      |

| $V_{OL1}$                            | Output Low Voltage<br>(SDA/D <sub>0</sub> -D <sub>7</sub> , OSC2)                             | I <sub>out</sub> =100mA                                                                                                                                                             | 0                   | -               | 0.1*V <sub>DD</sub>  | ٧      |

| $V_{R1}$                             | LCD Driving Voltage Source (V <sub>R</sub> Pin)                                               | Voltage Regulator Enabled ( $V_R$ voltage depends on TC and Int/Ext Contrast Control )                                                                                              | 0                   | -               | V <sub>CC</sub> -0.5 | ٧      |

| $V_{R3}$                             | LCD Driving Voltage Source (V <sub>R</sub> Pin)                                               | Regulated DC/DC Converter Mode                                                                                                                                                      | -                   | V <sub>CC</sub> | -                    | V      |

| $V_{R2}$                             | LCD Driving Voltage Source (V <sub>R</sub> Pin)                                               | Voltage Regulator & Regulated DC/DC Disabled.                                                                                                                                       | -                   | Floating        | -                    | V      |

| V <sub>CN</sub>                      | Internal Contrast Control (V <sub>R</sub> Output Voltage)                                     | Voltage Regulator Enabled, Internal Contrast control Enabled. (16 Voltage Levels Controlled by Software. )                                                                          | -5                  | -               | 5                    | %      |

SOLOMON REV 1.3 03/02 SSD1809

# $\textbf{ELECTRICAL CHARACTERISTICS} \ \, (\text{Voltage Referenced to V}_{\text{SS}}, \, \text{V}_{\text{DD}} = 2.2 \text{ to } 3.5 \text{V}, \, \text{T}_{\text{A}} = 25 ^{\circ} \text{ C}; \, \text{unless otherwise specified.})$

| Symbol                                                                                           | Parameter                                                                                                                               | Test Condition                                                                                      | Min                 | Тур                                                                                                    | Max                                                                                             | Unit             |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------|

| V <sub>IH1</sub>                                                                                 | Input high voltage<br>(RES, OSC2, CLK/WR/SCK,SDA/D <sub>0</sub> -D <sub>7</sub> , CE,<br>R/W/RD, D/C, P/S, 68/80, OSC1)                 |                                                                                                     | 0.8*V <sub>DD</sub> | -                                                                                                      | V <sub>DD</sub>                                                                                 | V                |

| V <sub>IL1</sub>                                                                                 | Input Low voltage<br>(RES, OSC2, CLK/WR/SCK,SDA/D <sub>0</sub> -D <sub>7</sub> , CE,<br>R/W/RD, D/C, P/S, 68/80, OSC1)                  |                                                                                                     | 0                   | -                                                                                                      | 0.2*V <sub>DD</sub>                                                                             | V                |

| V <sub>LL6</sub><br>V <sub>LL5</sub><br>V <sub>LL4</sub><br>V <sub>LL3</sub><br>V <sub>LL2</sub> | LCD Display Voltage Output<br>(V <sub>LL6</sub> , V <sub>LL5</sub> , V <sub>LL4</sub> , V <sub>LL3</sub> , V <sub>LL2</sub> Pins)       | Voltage Divider Enabled, 1:5 bias ratio                                                             | -<br>-<br>-<br>-    | V <sub>R</sub><br>4/5*V <sub>R</sub><br>3/5*V <sub>R</sub><br>2/5*V <sub>R</sub><br>1/5*V <sub>R</sub> | -<br>-<br>-<br>-                                                                                | V<br>V<br>V<br>V |

| V <sub>LL6</sub><br>V <sub>LL5</sub><br>V <sub>LL4</sub><br>V <sub>LL3</sub><br>V <sub>LL2</sub> | LCD Display Voltage Output (V <sub>LL6</sub> , V <sub>LL5</sub> , V <sub>LL4</sub> , V <sub>LL3</sub> , V <sub>LL2</sub> Pins)          | Voltage Divider Enabled, 1:7 bias ratio                                                             | -<br>-<br>-<br>-    | V <sub>R</sub><br>6/7*V <sub>R</sub><br>5/7*V <sub>R</sub><br>2/7*V <sub>R</sub><br>1/7*V <sub>R</sub> | -<br>-<br>-<br>-                                                                                | V<br>V<br>V<br>V |

| $\begin{array}{c} V_{LL6} \\ V_{LL5} \\ V_{LL4} \\ V_{LL3} \\ V_{LL2} \end{array}$               | LCD Display Voltage Input (V <sub>LL6</sub> , V <sub>LL5</sub> , V <sub>LL4</sub> , V <sub>LL3</sub> , V <sub>LL2</sub> Pins)           | Voltage Divider Enabled, 1:8 bias ratio                                                             | -<br>-<br>-<br>-    | V <sub>R</sub><br>7/8*V <sub>R</sub><br>6/8*V <sub>R</sub><br>2/8*V <sub>R</sub><br>1/8*V <sub>R</sub> | -<br>-<br>-<br>-                                                                                | V<br>V<br>V<br>V |

| V <sub>LL6</sub><br>V <sub>LL5</sub><br>V <sub>LL4</sub><br>V <sub>LL3</sub><br>V <sub>LL2</sub> | LCD Display Voltage Input (V <sub>LL6</sub> , V <sub>LL5</sub> , V <sub>LL4</sub> , V <sub>LL3</sub> , V <sub>LL2</sub> Pins)           | Voltage Divider Enabled, 1:9 bias ratio                                                             | -<br>-<br>-<br>-    | V <sub>R</sub><br>8/9*V <sub>R</sub><br>7/9*V <sub>R</sub><br>2/9*V <sub>R</sub><br>1/9*V <sub>R</sub> | -<br>-<br>-<br>-                                                                                | V<br>V<br>V<br>V |

| V <sub>LL6</sub><br>V <sub>LL5</sub><br>V <sub>LL4</sub><br>V <sub>LL3</sub><br>V <sub>LL2</sub> | LCD Display Voltage Input (V <sub>LL6</sub> , V <sub>LL5</sub> , V <sub>LL4</sub> , V <sub>LL3</sub> , V <sub>LL2</sub> Pins)           | External Voltage Generator, Voltage Divider Disable                                                 | 7<br>0<br>0<br>0    | -<br>-<br>-<br>-                                                                                       | V <sub>CC</sub><br>V <sub>LL6</sub><br>V <sub>LL5</sub><br>V <sub>LL4</sub><br>V <sub>LL3</sub> | V<br>V<br>V<br>V |

| I <sub>OH</sub>                                                                                  | Output High Current Source<br>(SDA/D <sub>0</sub> -D <sub>7</sub> , OSC2)                                                               | V <sub>out</sub> =V <sub>DD</sub> -0.4V                                                             | 50                  | -                                                                                                      | -                                                                                               | μА               |

| I <sub>OL</sub>                                                                                  | Output Low Current Drain<br>(SDA/D <sub>0</sub> -D <sub>7</sub> , OSC2)                                                                 | V <sub>out</sub> =0.4V                                                                              | -                   | -                                                                                                      | -50                                                                                             | μА               |

| I <sub>OZ</sub>                                                                                  | Output Tri-state Current Drain Source (SDA/D <sub>0</sub> -D <sub>7</sub> , OSC2)                                                       |                                                                                                     | -1                  | -                                                                                                      | 1                                                                                               | μΑ               |

| I <sub>IL</sub> /I <sub>IH</sub>                                                                 | Input Current (RES, OSC2, CLK/WR/SCK,SDA/D <sub>0</sub> -D <sub>7</sub> , CE, R/W/RD, D/C, P/S, 68/80, OSC1)                            |                                                                                                     | -1                  | -                                                                                                      | 1                                                                                               | μΑ               |

| R <sub>on</sub>                                                                                  | Channel resistance between LCD driving signal pins (SEG and COM) and driving voltage input pins (V <sub>LL2</sub> to V <sub>LL6</sub> ) | During Display on, 0.1V apply between two terminals, V <sub>CC</sub> within operating voltage range | -                   | -                                                                                                      | 10                                                                                              | kΩ               |

| $V_{SB}$                                                                                         | Memory Retention Voltage (DV <sub>DD</sub> )                                                                                            | Standby mode, retain all internal configuration and RAM data                                        | 2                   | -                                                                                                      | -                                                                                               | V                |

| C <sub>IN</sub>                                                                                  | Input Capacitance<br>(OSC1, OSC2, all logic pins)                                                                                       |                                                                                                     | -                   | 5                                                                                                      | 7.5                                                                                             | pF               |

| PTC0<br>PTC3                                                                                     | Temperature Coefficient Compensation* Flat Temperature Coefficient Temperature Coefficient 3*                                           | TC1=0, TC2=0, Voltage Regulator Disabled TC1=1, TC2=1, Voltage Regulator Enabled                    | -                   | 0.0<br>-0.35                                                                                           | -<br>-                                                                                          | %<br>%           |

<sup>\*</sup>The formula for the temperature coefficient (TC) is:

$$TC(\%) = \frac{V_R \text{ at } 50^{\circ} \text{ C} - V_R \text{ at } 0^{\circ} \text{ C}}{50^{\circ} \text{ C} - 0^{\circ} \text{ C}} \times \frac{1}{V_R \text{ at } 25^{\circ} \text{ C}} \times 100\%$$

# $\textbf{AC ELECTRICAL CHARACTERISTICS} \ (Voltage \ Referenced \ to \ V_{SS}, V_{DD} = 2.2 \ to \ 3.5 V, \ T_A = 25 ^{\circ} \ C; \ unless \ otherwise \ specified.)$

| Symbol           | Parameter                                                                     | Test Condition                                                                                                                                                               | Min                                                                                                                                                               | Тур                                                                 | Max                          | Unit                 |

|------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------|----------------------|

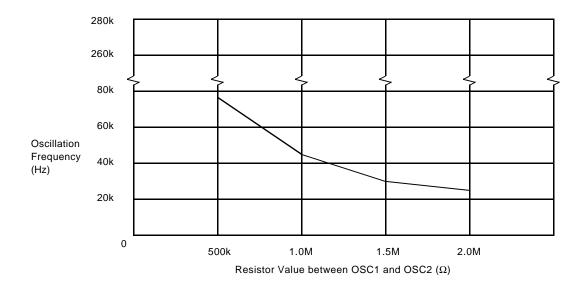

| F <sub>OSC</sub> | Oscillation Frequency of Display timing generator                             | Resistor between OSC1 andOSC2 is 900k W<br>Internal Oscillator Enabled                                                                                                       | -                                                                                                                                                                 | 50                                                                  | -                            | kHz                  |

| F <sub>FRM</sub> | Frame Frequency in Graphic / Character Display Mode                           | Normal Display Frequency Half Display Frequency                                                                                                                              | Fosc / [2 x Mux Ratio x (Frame Freq Register Fosc / [4 x Mux Ratio x (Frame Freq Register                                                                         |                                                                     | ,,                           |                      |

|                  | Frame Frequency in Low Power Icon<br>Mode                                     | Icon Mode A and Normal Display Frequency<br>Icon Mode B and Normal Display Frequency<br>Icon Mode C and Normal Display Frequency<br>Icon Mode D and Normal Display Frequency | Fosc /<br>Fosc /                                                                                                                                                  | / [48 x (Frame<br>/ [64 x (Frame<br>/ [96 x (Frame<br>[144 x (Frame | Freq Registe<br>Freq Registe | er + 1)]<br>er + 1)] |

| Icon M           |                                                                               | Icon Mode A and Half Display Frequency<br>Icon Mode B and Half Display Frequency<br>Icon Mode C and Half Display Frequency<br>Icon Mode D and Half Display Frequency         | Fosc / [96 x (Frame Freq Register +1)] Fosc / [128 x (Frame Freq Register + 1)] Fosc / [192 x (Frame Freq Register + 1)] Fosc / [288 x (Frame Freq Register + 1)] |                                                                     | er + 1)]<br>er + 1)]         |                      |

| osc              | Internal Oscillation Frequency with dif-<br>ferent value of feedback resistor | Internal Oscillator Enabled, V <sub>DD</sub> within operation range                                                                                                          | Se                                                                                                                                                                | e Figure 1 for                                                      | the relations                | hip                  |

Figure 1 : Internal Oscillator Frequency Relationship with External Resistor Value at  $V_{DD} = 3V$

SOLOMON REV 1.3 SSD1809 33/02 SSD1809

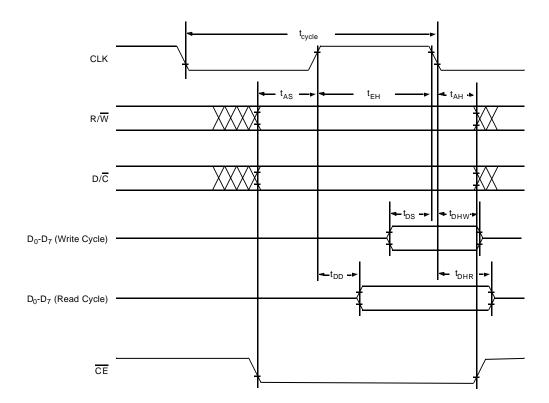

$\textbf{Table 1: Timing Characteristics for 6800-Series Parallel Interface} \ (T_{A}\text{=-}30 \text{ to } 85^{o}\text{C}, \ DV_{DD}\text{=-}2.2 \text{ to } 3.5\text{V}, \ V_{SS}\text{=-}0\text{V})$

| Symbol             | Parameter                       | Min  | Тур | Max | Unit |

|--------------------|---------------------------------|------|-----|-----|------|

| t <sub>cycle</sub> | Enable Cycle Time               | 1000 | -   | -   | ns   |

| t <sub>EH</sub>    | Enable Pulse Width              | -    | 500 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time              | -    | 200 | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time               | -    | 250 | -   | ns   |

| t <sub>DS</sub>    | Data Setup Time for Write Cycle | -    | 350 | -   | ns   |

| $t_DHW$            | Data Hold Time for Write Cycle  | -    | 250 | -   | ns   |

| t <sub>DD</sub>    | Data Delay Time for Read Cycle  | -    | 350 | -   | ns   |

| t <sub>DHR</sub>   | Data Hold Time for Read Cycle   | -    | 100 | -   | ns   |

Figure 2 : Timing Characteristics for 6800-Series Parallel Interface

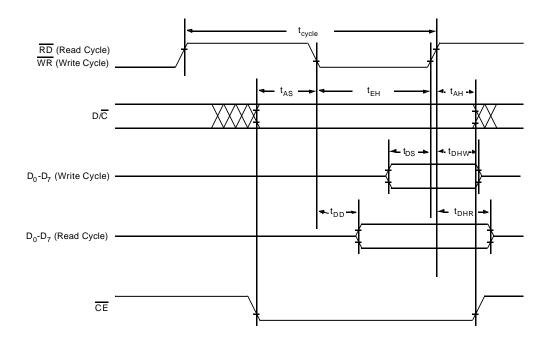

$\textbf{Table 2: Timing Characteristics for 80-Series Parallel Interface} \ (\textbf{T}_{A}\text{=-30 to }85^{o}\text{C},\ \textbf{DV}_{DD}\text{=-2.2 to }3.5\text{V},\ \textbf{V}_{SS}\text{=-0V})$

| Symbol             | Parameter                       | Min  | Тур | Max | Unit |

|--------------------|---------------------------------|------|-----|-----|------|

| t <sub>cycle</sub> | Enable Cycle Time               | 1000 | -   | -   | ns   |

| t <sub>EH</sub>    | Enable Pulse Width              | -    | 500 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time              | -    | 200 | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time               | -    | 250 | -   | ns   |

| t <sub>DS</sub>    | Data Setup Time for Write Cycle | -    | 350 | -   | ns   |

| t <sub>DHW</sub>   | Data Hold Time for Write Cycle  | -    | 250 | -   | ns   |

| t <sub>DD</sub>    | Data Delay Time for Read Cycle  | -    | 350 | -   | ns   |

| t <sub>DHR</sub>   | Data Hold Time for Read Cycle   | -    | 100 | -   | ns   |

Note: In Read Cycle, the  $\overline{\text{WR}}$  pin should be High. In Write Cycle, the  $\overline{\text{RD}}$  pin should be High.

Figure 3 : Timing Characteristics for 80-Series Parallel Interface

REV 1.3 SSD1809 **SOLOMON**

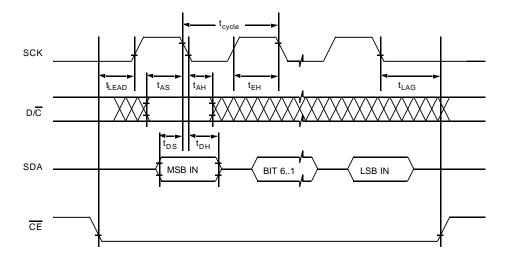

$\textbf{Table 3: Timing Characteristics for Serial Peripheral Interface (SPI)} \ (T_A = -30 \ to \ 85^{\circ}C, \ DV_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_{DD} = 2.2 \ to \ 3.5 \ V_{SS} = 0 \ V_$

| Symbol             | Parameter          | Min  | Тур | Max | Unit |

|--------------------|--------------------|------|-----|-----|------|

| t <sub>cycle</sub> | Enable Cycle Time  | 1000 | -   | -   | ns   |

| t <sub>EH</sub>    | Enable Pulse Width | -    | 500 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time | -    | 200 | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time  | -    | 250 | -   | ns   |

| t <sub>DS</sub>    | Data Setup Time    | -    | 350 | -   | ns   |

| t <sub>DH</sub>    | Data Hold Time     | -    | 250 | -   | ns   |

| t <sub>LEAD</sub>  | Enable Lead Time   | -    | 350 | -   | ns   |

| t <sub>LAG</sub>   | Enable Lag Time    | -    | 100 | -   | ns   |

Figure 4: Timing Characteristics for Serial Peripheral Interface (SPI)

# PIN DESCRIPTIONS

# P/S (Parallel / Serial Interface)

This pin is an input pin which is used to select parallel interface or serial interface. Input High for parallel interface (6800 or 80) while input Low for serial interface (SPI).

# 68/80

This pin is an input pin which is used to select 6800 interface or 80 interface. Input High for 6800 interface while input Low for 80 interface.

# D/C (Data / Command)

This input pin acknowledges the LCD driver that the input at SDA/D<sub>0</sub>-D7 is data or command. Input High for data while input Low for command.

### CE (Chip Enable)

This pin is an input pin. The chip is enabled when this pin is Low.

### CLK/ WR / SCK

When 6800-series parallel interface is selected, this input pin is named as CLK which is a clock. Data on SDA/D $_0$ -D $_7$  are latched at the falling edge of CLK.

When 80-series parallel interface is selected, this input pin is named as WR which is a clock in write cycle. It is low enable for write data/ command and data on SDA/D<sub>0</sub>-D<sub>7</sub> are latched at the rising edge of WR. In read cycle, this pin should be High.

When SPI is selected, this input pin is named as SCK which is a serial clock. Data on SDA /D<sub>0</sub> is latched at the falling edge of SCK.

### **RES (Reset)**

An active Low pulse to this pin reset the internal status of the driver (same as power on reset). The minimum pulse width is 1  $\mu s$  to initiate the reset process.

# SDA / D<sub>0</sub>-D<sub>7</sub> (Data)

SDA/Do-D7 is a bi-directional bus and is used for data/command transfer. If 6800-series or 80-series parallel interface is selected, D<sub>0</sub>-D<sub>7</sub> are connected directly to MCU for data transfer.

When SPI is selected, Do is named as SDA which is a serial input of the driver. It receives data/command from MCU to driver and transfers serially. Meanwhile, D<sub>1</sub>-D<sub>7</sub> pins can be High or Low.

# R/W / RD

When 6800-series parallel interface is selected, this input pin is named as R/W, Input High will read the display data RAM or the internal status (Busy/Idle) while input Low will write the display data RAM or the internal setup registers.

When 80-series parallel interface is selected, this input pin is named as RD and is a clock in read cycle. It is low enable for read data/command and data SDA/D<sub>0</sub>-D<sub>7</sub> are latched at the rising edge of RD. In write cycle, this pin should be High.

When SPI is selected, this input pin can be High or Low.

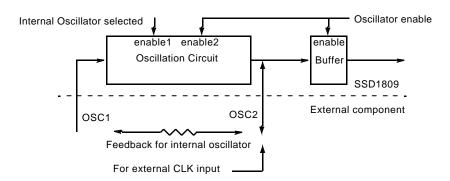

# **OSC1 (Oscillator Input)**

For internal oscillator mode, this is an input pin for the internal low power RC oscillator circuit. In this mode, an external resistor of certain value should be connected between the OSC1 and OSC2 pins for a range of internal operating frequencies (refer to Figure 1). For external oscillator mode, OSC1 should be left open.

# OSC2 (Oscillator Output / External Oscillator Input)

For internal oscillator mode, this is an output for the internal low power RC oscillator circuit. For external oscillator mode, OSC2 will be an input pin for external clock and no external resistor is needed.

V<sub>LL6</sub> - V<sub>LL2</sub>

Group of voltage level pins for driving the LCD panel. They can either be connected to external driving circuit for external bias supply or connected internally to built-in divider circuit if internal divider is enable. For internal Voltage Generator enabled, a 1.0 µF capacitor to AVSS is required on each pin.

# DUM1 - DUM4

If the internal bias voltage levels generator is enabled, a  $1\mu\text{F}$ capacitor to AV<sub>SS</sub> is required on each pin.

# $C_{1N}$ and $C_{1P}$ , $C_{2N}$ and $C_{2P}$ , $C_{3N}$ and $C_{3P}$

If internal Voltage Generator is enabled with 2X DC-DC converter, a  $0.1 \mu F$  capacitor is required to connect between  $C_{1N}$  &  $C_{1P}$ .

If internal Voltage Generator is enabled with 3X/4X DC-DC converter, a  $0.1\mu F$  capacitor is required to connect between  $C_{1N}$  &  $C_{1P}$  and C<sub>3N</sub> & C<sub>3P</sub>.

If internal Voltage Generator is enabled with 5X DC-DC converter, a 0.1μF capacitor is required to connect these three pair of pins.

### C+ and C-

If internal divider circuit is enabled, a  $1\mu F$  capacitor is required to connect between these two pins.

# $\rm V_R$ and $\rm V_F$

This is a feedback path for the gain control (external contrast control) of V<sub>LL2</sub> to V<sub>LL6</sub>. For adjusting the LCD driving voltage, it requires a feedback resistor placed between V<sub>R</sub> and V<sub>F</sub>, a gain control resistor placed between  $V_{\!F}$  and  $AV_{\!SS},$  a 4.7  $\!\mu F$  capacitor placed between  $V_{\!R}$  and AV<sub>SS</sub>. (Refer to the Application Circuit)

### COM0-COM64 (Row Drivers)

These lines provide the LCD row driving signals to the LCD panel. COM64 also serves as the common driving signal in the icon mode. Output is 0V during display off.

# SEG0-SEG159 (Column Drivers)

These 160 pins provide LCD column driving signal to LCD panel. Output is 0V during display off.

# $AV_{DD}$ and $AV_{SS}$

AV<sub>DD</sub> and AV<sub>SS</sub> are the positive supply and ground to all of the analog circuit respectively.

# $v_{cc}$

For using the internal Voltage Generator, a 0.1µF capacitor from this pin to AV<sub>SS</sub> is required. It can also be an external bias input pin if internal Voltage Generator is not used. Power is supplied to the LCD Driving Level Selector and HV Buffer Cell with this pin. Normally, this pin is not intended to be a power supply to other components.

# $\mathrm{DV}_{\mathrm{DD}}$ and $\mathrm{DV}_{\mathrm{SS}}$

Power is supplied to the digital control circuit and DC/DC converter of the driver using these two pins. DV<sub>DD</sub> is power and DV<sub>SS</sub> is ground.

# $V_{DC}$

V<sub>DC</sub> is the power supply to the DC/DC converter of the driver.

Remark: In SSD1809T TAB package,  $V_{DC}$  pin is connected to  $DV_{DD}$ and P/S pin & 68/80 pin are connected to  $AV_{DD}$ . Only 6800-parallel interface can be used and DV<sub>DD</sub> will be the supply of the DC/DC converter in this package.

SOLOMON **REV 1.3** SSD1809 03/02 11

# **OPERATION OF LIQUID CRYSTAL DISPLAY DRIVER**

# **Description of Block Diagram Module**

### Command Decoder and Command Interface

This module determines whether the input data is interpreted as data or command. Data is directed to this module based upon the input of the D/ $\overline{C}$  pin. If D/ $\overline{C}$  is high, data is written to Graphic Display Data RAM (GDDRAM). If D/ $\overline{C}$  is low, the input at SDA/D<sub>0</sub>-D<sub>7</sub> is interpreted as a Command and it will be decoded and written to the corresponding command register.

Reset is of the same function as Power ON Reset (POR). Once  $\overline{RES}$  receives a negative reset pulse of minimium 1 $\mu$ s, all internal circuit will be back to its initial status.

### MPU 6800-series Parallel Interface

The parallel interface consists of 8 bi-directional data pins  $(D_0^-D_7)$ ,  $R/\overline{W}$ ,  $D.\overline{C}$ ,  $\overline{CE}$ , and CLK.  $R/\overline{W}$  input High indicates a read operation from the Graphic Display Data RAM (GDDRAM) or the status register.  $R/\overline{W}$  input Low indicates a write operation to Display Data RAM or Internal Command Registers depending on the status of  $D/\overline{C}$  input. The chip is enabled when the  $\overline{CE}$  is low and the CLK input serves as data latch signal (clock). Refer to Figure 2 showing timing characteristics for 6800-series parallel interface.

### MPU 80-Series Parallel Interface

The parallel interface consists of 8 bi-directional data pins (D $_0$ -D $_7$ ),  $\overline{RD}$ ,  $\overline{WR}$ , D/ $\overline{C}$ , and  $\overline{CE}$ .  $\overline{RD}$  input serves as data read latch signal (clock) provided that  $\overline{CE}$  is  $\underline{low}$ .  $\overline{WR}$  input serves as data write latch signal(clock) provided that  $\overline{CE}$  is  $\underline{low}$ . Whether it is display data or command register write is controlled by D/ $\overline{C}$ . Refer to Figure 3 showing timing characteristics for 80-series parallel interface.

# MPU Serial Peripheral Interface

The serial interface consists of serial clock SCK, serial data SDA,  $D/\overline{C}$ , and  $\overline{CE}$ . The chip is enabled when  $\overline{CE}$  is low and SDA is shifted into a 8-bit shift register on every falling edge of SCK and data are transferred serially with MSB first and LSB last.  $D/\overline{C}$  is sampled on every first clock of each byte cycle and the information is interpreted as Display Data or Command accordingly.

The eight bits information from SDA pin are stored in a buffer shift register. After the next byte information from SDA pin is written into the buffer, the original contents in the buffer will be sent to Display Data RAM or Command Register. A No-Operation (01101000) command could be written to push the last information in the buffer into Display RAM or Command Register.

The first bit after the  $\overline{\text{CE}}$  pin falling edge or the  $\overline{\text{RES}}$  pin rising edge is always interpreted as MSB.

Refer to Figure 4 showing timing characteristics for Serial Peripheral Interface.

### Selection of Interface

Selection of the desired interface is done by putting  $P/\overline{S}$  and  $68/\overline{80}$  either high or low as shown in the following table:-

| PIN   | 6800-Series | 80-Series | SPI      |

|-------|-------------|-----------|----------|

| P/S   | High        | High      | Low      |

| 68/80 | High        | Low       | High/Low |

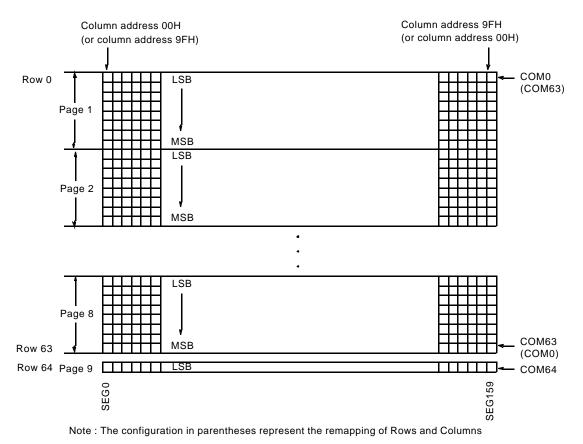

Figure 5: Graphic Display Data RAM (GDDRAM) Address Map

# Graphic Display Data RAM (GDDRAM)

The GDDRAM is a bit mapped static RAM holding the bit pattern to be displayed. The size of the RAM is determined by number of row times the number of column (160x65 = 10400 bits). Figure 5 is a description of the GDDRAM address map. For mechanical flexibility, re-mapping on both Segment and Common outputs are provided.

# **Display Timing Generator**

This module is an on chip low power RC oscillator circuitry (Figure 6). The oscillator frequency can be selected in the range of 25kHz to 200kHz by external resistor. One can enable the circuitry by software command. For external clock provided, feed the clock to OSC2 and leave OSC1 open.

Figure 6: Oscillator Circuitry

### LCD Driving Voltage Generator and Regulator

This module generates the LCD voltage needed for display output. It takes a single supply input and generate necessary bias voltages. It consists of:

# 1. 2X, 3X, 4X and 5X DC-DC Converter

To generate the V<sub>CC</sub> voltage. 2X, 3X and 4X DC-DC converter are used for LCD panel which needs lower driving voltage for less power consumption. 5X DC-DC converter is used for LCD panel which needs higher driving voltage.

# 2. Voltage Regulator

Feedback gain control for initial LCD voltage. it can also be used with external contrast control.

# 3. Voltage Divider

Divide the LCD display voltage (V<sub>LL2</sub>-V<sub>LL6</sub>) from the regulator output. This is a low power consumption circuit which can save the most display current compare with traditional resistor ladder method.

# 4. Self adjust temperature compensation circuitry

Provide 2 different compensation grade selections to satisfy the various liquid crystal temperature grades. The grading can be selected by software control.

# 5. Contrast Control Block

Software control of 16 voltage levels of LCD voltage.

All blocks can be individually turned off if external voltage generator is employed.

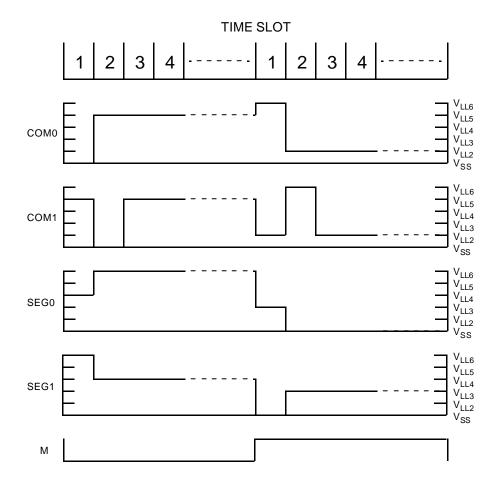

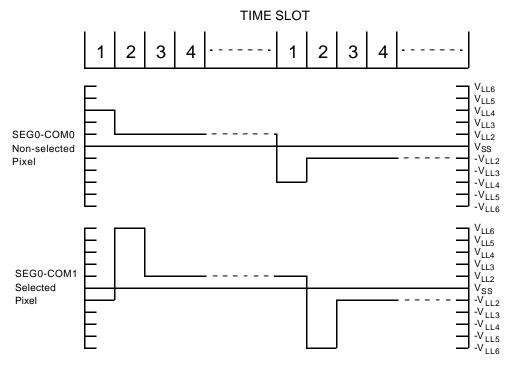

### 65 Bit Latch / 160 Bit Latch

A 225 bit long register which carries the display signal information. First 65 bits are Common driving signals and other 160 bits are Segment driving signals. Data will be input to the HV-buffer Cell for bumping up to the required level.

### **Level Selector**

Level Selector is a control of the display synchronization. Display voltage can be separated into two sets and used with different cycles. Synchronization is important since it selects the required LCD voltage level to the HV Buffer Cell for output signal voltage pump.

# HV Buffer Cell (Level Shifter)

HV Buffer Cell works as a level shifter which translates the low voltage output signal to the required driving voltage. The output is shifted out with an internal FRM clock which comes from the Display Timing Generator. The voltage levels are given by the level selector which is synchronized with the internal M signal.

Figure 7a: LCD Display Example "0"

SOLOMON **REV 1.3** SSD1809 03/02 13

Figure 7b: LCD Driving Signal from SSD1809

Figure 7c: Effective LCD waveform on LCD pixel

# **Command Description**

# Display On (Display Mode)

This command turns the LCD Common and Segment outputs on. This command starts the conversion of data in GDDRAM to necessary waveforms on the Common and Segment driving outputs. The on-chip bias generator is also turned on by this command. (Note: "Oscillator On" command should be sent before "Display On" is selected)

# Display Off (Stand-by Mode)

This command turns the display off and the states of the LCD driver are as follow during display off :

- 1. The Common and Segment outputs are fixed at  $V_{SS}$ .

- 2. The Bias Voltage Generator is turned off.

- 3. The RAM and content of all registers are retained.

- 4. IC will accept new commands and data.

The Oscillator is not affected by this command.

# Set GDDRAM Column Address

This command positions the address pointer on a column location. The address can be set to location 00H-9FH (160 columns) and the MSB is software set by "set MSB of GDDRAM Column Address". The column address will be increased automatically after a read or write operation. Refer to "Address Increment Table" and command "Set GDDRAM Page Address" for further information.

# Set GDDRAM Page Address

This command positions the row address to 1 of 9 possible positions in GDDRAM. Refer to figure 5.

### Save / Restore Column Address

Save Column Address command saves a copy of the Column Address of GDDRAM. Restore Column Address command restores the copy obtained from the previous execution of saving column address. This instruction is very useful for writing full graphics characters that are larger than 8 pixels vertically.

# Master Clear GDDRAM

This command is to clear the content of the Display Data RAM to zero. Issue this command followed by a dummy write data.

# Master Clear Icon RAM

This command is used to clear the content of the Icon Data RAM to zero. Set the page pointer to icon page (page 9) and then issue this command followed by a dummy write data.

# Set Page Mask

This command is used to define the page which will be masked. Once the command "Set Page Mask" is issued, the next command will be written to the Page Mask Register which is an 8-bit register. Each bit represents one of the 8 pages: page mask bit 0 represents Page 1, page mask bit 1 represents Page 2, ... etc.

# **Enable Page Mask**

When the Page Mask is enabled, the display of those pages, with page mask bit set, will be cleared. Meanwhile, the data in the display RAM is retained

# **Enable Icon Mask**

When the Icon Mask is enabled, the display of the icons will be cleared. Meanwhile, the data in the icon display RAM is retained.

# Set Logical Page Mask

This command is used to select the page mask type. There are two page mask types 1) Physical page mask and 2)Logical page mask. Physical mask refers to a physical location of the panel which cannot be moved by scrolling, row remap or panel offset. Logical page mask refers to the location of GDDRAM. Therefore a logical mask will keep masking a definite area of GDDRAM content when the contain is moved along the panel by scrolling, row remap or panel offset.

### Set Display Mode

This command switches the driver to full display mode or icon display mode. In low power icon mode, only icons (driven by COM64) are displayed. The DC-DC converter, the voltage generator and the regulator are disabled. All  $V_{CC}$ ,  $V_{LL}$ s pins cannot have external bias voltage supply in the low power icon mode. Refer " Set Icon Mode" for further information.

### Set Icon Mode

This command is used to select one of 4 smart icon modes.

In smart icon mode A, on-pixels are stressed by a voltage with root-mean-square value of  $1xV_{DD}$  whereas off-pixels by  $0.58xV_{DD}$ .

In smart icon mode B, on-pixels are stressed by a voltage with root-mean-square value of  $0.87 \text{xV}_{DD}$  whereas off-pixels by  $0.5 \text{xV}_{DD}$ .

In smart icon mode C, on-pixels are stressed by a voltage with root-mean-square value of  $0.71 \text{xV}_{DD}$  whereas off-pixels by  $0.41 \text{xV}_{DD}$ .

In smart icon mode D, on-pixels are stressed by a voltage with root-mean-square value of  $0.58 \text{xV}_{DD}$  whereas off-pixels by  $0.33 \text{xV}_{DD}$ .

Remark: Icon Mode cannot be used if external divider is used.

### Set Display Frequency

In half display frequency mode, the display frame frequency will be halved. Also, the operation frequency of analog circuitries will be halved as well.

# Set Frame Frequency

This command is used to select one of 16 frame frequencies from Fosc/(2 x Mux Ratio) to Fosc/(32 x Mux Ratio). When the "Frame Frequency "command is issued, the following command will be written to the "Frame Frequency Register" which is used to define the desired frame frequencies.

# Set Bias Ratio

This command sets the bias of 1:5, 1:7, 1:8 or 1:9 bias for the divider output. The selection should match the characteristic of LCD Panel.

# Oscillator Enable

This command is used to either turn on / off Oscillator. For using internal or external oscillator, this command should be executed. The setting for this command is not affected by command " Set Display On/ Off" . See command " Ext/Int Oscillator" for more information

# Ext / Int Oscillator

This command is used to select either internal or external oscillator. When internal oscillator is selected, feedback resistor between OSC1 and OSC2 is needed. For external oscillation circuit, feed clock input signal to OSC2 and leave OSC1 open.

# **Voltage Generator Enable**

This command is used to enable the internal Voltage Generator to generate the  $V_{CC}$  from  $AV_{DD}$ . Disable the voltage generator if external

SOLOMON REV 1.3 SSD1809

Vcc is provided.

# Set 2X / 3X / 4X / 5X Converter

This command selects the usage of 2X / 3X / 4X / 5X Converter when the internal voltage Generator is enabled.

### Set DC/DC Converter Mode

This command sets the DC/DC converter to regulated mode. In regulated mode, V<sub>CC</sub> voltage equals to V<sub>R</sub> voltage.

### Voltage Regulator Enable

This command enables regulator which consists of the internal contrast control and temperature compensation circuits.

### Internal Voltage Divider Enable

If the internal divider is disabled, external bias can be used for V<sub>LL6</sub> to V<sub>LL2.</sub> If the internal divider is enabled, the internal circuit will generated the 1:5 / 1:7 / 1:8 / 1:9 bias driving voltage.

### **Internal Contrast Control Enable**

This command is used to adjust the delta voltage of the bias voltages. With bit option = 1, the software selection for delta bias voltage control is enabled. With bit option = 0, internal contrast control is dis-

### Increase / Decrease Contrast Level

If the internal contrast control is enabled, this command is used to increase or decrease the contrast level within the 16 contrast levels.

### Set Contrast Level

This command is used to select one of the 16 contrast levels from 10h to 1Fh when internal contrast control circuitry is in use.

### **Set Temperature Coefficient**

This command can select 2 different LCD driving voltage temperature coefficients to match various liquid crystal temperature grades. Those temperature coefficients are specified in Electrical Characteristics Tables.

# Set MUX Ratio / Chinese Character Mode (Partial Display)

This command is used to select the Graphic display mode with different Mux from 2 Mux to 65 Mux or the Chinese character display mode with different character line from 1 line to 3 lines. Figure 8a & 8b in the section "Display Output Description" show the 65 Mux Graphic display mode and 3-line Chinese character display mode respectively.

### Set Row Re-Mapping

This instruction selects the mapping of Display Data RAM to Common drivers for mechanical flexibility. There are 2 mappings:

- 1. Row(0) Row(Mux ratio-2) of GDDRAM mapped to COM(first display row location) - COM( first display row location+Mux ratio-2). Example is illustrated in figure 8b, the first display row location is COM0 and the Mux ratio is 53, then Row0 of GDDRAM wil be mapped to COM0, Row1 through Row 51 of GDDRAM will be mapped to COM1 to COM51.

- 2. Row(0) Row(Mux ratio-2) of GDDRAM mapped to COM(first display row location+Mux ratio-2) - COM(first display row location). Example is illustrated in figure 8c, Row0 - Row51 of GDDRAM is mapped to COM51 - COM0.

# Set Column Re-Mapping

This instruction selects the mapping of new Display Data RAM to Segment drivers for mechanical flexibility. There are 2 mappings to select:

- 1. Column 0 Column 159 of GDDRAM mapped to SEG0-SEG159 respectively;

- 2. Column 0 Column 159 of GDDRAM mapped to SEG159-SEG0 respectively.

Detailed information please refer to Figure 8d in the section "Display Output Description".

# Set Vertical Scroll Value

In Graphic display mode, this command maps the selected GDDRAM rows (00H-3FH) to COM pins. With scroll value equals to 0, Row 0 of GDDRAM is mapped to COM0 and Row 1 through Row 63 are mapped to COM1 through COM63 respectively. With scroll value equal to 1, Row 1 of GDDRAM is mapped to COM0, then Row 2 through Row 63 will be mapped to COM1 through COM62 respectively and Row 0 will be mapped to COM63.

In Chinese character display mode, there are 73 rows of display content including space and icon. This command moves the display content downward equals to the value stored vertical scrolling register.

# **Set Display Rows Location**

This command is used to define the first row location of the display, the first row can be started at COM0 to COM63. Example is given in Figure 8h.

SOLOMON SSD1809 **REV1.3** 03/02

# **Display Output Description**

This is an example of output pattern on the LCD panel. Figure 8a shows the content in GDDRAM and Figure 8b - 8h illustrate the output patterns on the LCD display with a sequence of commands:

- 1) Set 3-line Chinese character display mode shown in Figure 8b,

- 2) Enable row re-mapping shown in Figure 8c,

- 3) Enable column re-mapping & rewrite RAM content shown in Figure 8d,

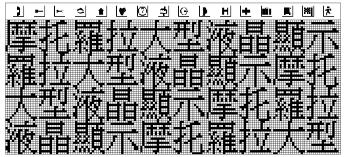

Figure 8a: Content in GDDRAM

Figure 8b: 3-line Chinese character mode

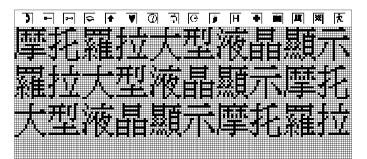

Figure 8c: Row remap enable

Figure 8d: Column remap enable & Re-write RAM content

- 4) Enable vertical scrolling command with scrolling value of 07h shown in Figure 8e,

- 5) Disable row re-mapping & column re-mapping and rewrite map content shown in Figure 8f,

- 6) Enable vertical scrolling command with scrolling value of 3Eh shown in Figure 8g and

- 7) Set display rows location at 06h shown in Figure 8h.

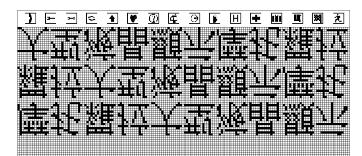

Figure 8e: Vertical scrolling with writing 07h to scrolling register

Figure 8f: Disable row re-mapping & column re-mapping and Rewrite map content.

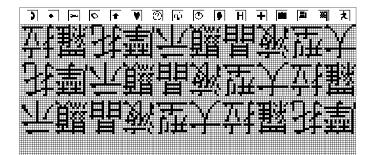

Figure 8g: Vertical scrolling with writing 3Eh to scrolling register

Figure 8h: Centering with display rows location 06h

**SOLOMON** SSD1809 **REV 1.3**

# **COMMAND TABLE**

| Bit Pattern                                                     | Command                               | Comment                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | Set GDDRAM Page Address               | Set GDDRAM Page Address using $X_3X_2X_1X_0$ as address bits. $X_3X_2X_1X_0$ =0000 : page 1 (POR) $X_3X_2X_1X_0$ =0001 : page 2 $X_3X_2X_1X_0$ =0010 : page 3 $X_3X_2X_1X_0$ =0011 : page 4 $X_3X_2X_1X_0$ =0100 : page 5 $X_3X_2X_1X_0$ =0101 : page 6 $X_3X_2X_1X_0$ =0111 : page 7 $X_3X_2X_1X_0$ =0111 : page 8 $X_3X_2X_1X_0$ =1000 : page 9 |

| 00001001                                                        | Set Display Rows Location             | Next Command (byte) on $D_5 \sim D_0$ defines the display rows location.<br>Starts at Row0 - COM0 (POR)                                                                                                                                                                                                                                           |

| 0000101X <sub>0</sub>                                           | Set 2X/3X DC-DC Converter             | $\rm X_0$ =0 : Enable 2X Converter $\rm X_0$ =1 : Enable 3X Converter Remark: This command overrides "Set 4X/5X DC-DC Converter" .                                                                                                                                                                                                                |

| 000011 X <sub>1</sub> X <sub>0</sub>                            | Reserved                              |                                                                                                                                                                                                                                                                                                                                                   |

| 00001110                                                        | Reserved                              |                                                                                                                                                                                                                                                                                                                                                   |

| 0001X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | Set Contrast Level                    | Set one of the 16 contrast level values using $\rm X_3X_2X_1X_0$ as data bits. Reset to 0000 during POR.                                                                                                                                                                                                                                          |

| 00001111                                                        | Reserved                              |                                                                                                                                                                                                                                                                                                                                                   |

| 0010000X <sub>0</sub>                                           | Set 4X / 5X DC-DC Converter           | $\rm X_0$ =0: Enable 4X Converter (POR) $\rm X_0$ =1: Enable 5X Converter Remark: This command overrides "Set 2X/3X DC-DC Converter" .                                                                                                                                                                                                            |

| 0010001X <sub>0</sub>                                           | Set Segment Re-Mapping                | $X_0=0$ : Column 0 to SEG0 (POR)<br>$X_0=1$ : Column 0 to SEG159                                                                                                                                                                                                                                                                                  |

| 0010010X <sub>0</sub>                                           | Set Common Re-Mapping                 | $X_0$ =0 : Row 0 to Display Row location (POR) $X_0$ =1: Flip the Row-COM mapping.                                                                                                                                                                                                                                                                |

| 0010011X <sub>0</sub>                                           | Set MSB of GDDRAM Column<br>Address   | $X_0$ =0: MSB = 0 (POR)<br>$X_0$ =1: MSB = 1                                                                                                                                                                                                                                                                                                      |

| 0010100X <sub>0</sub>                                           | Set Display on/off                    | X <sub>0</sub> =0: Display off (POR)<br>X <sub>0</sub> =1: Display on                                                                                                                                                                                                                                                                             |

| 0010101X <sub>0</sub>                                           | Voltage Generator Enable              | $X_0$ =0: Disable Voltage Generator (POR)<br>$X_0$ =1: Enable Voltage Generator                                                                                                                                                                                                                                                                   |

| 0010110X <sub>0</sub>                                           | Voltage Regulator Enable              | $\rm X_0$ =0: Disable Regulator (POR) $\rm X_0$ =1: Enable Regulator When application uses a supply with built-in temperature compensation, the regulator should be disabled.                                                                                                                                                                     |

| 0010111X <sub>0</sub>                                           | Voltage Divider Enable                | $\rm X_0$ =0: Disable Voltage Divider (POR) $\rm X_0$ =1: Enable Voltage Divider When an external bias network is preferred, the voltage divider should be disabled.                                                                                                                                                                              |

| 0011000X <sub>0</sub>                                           | Internal Contrast Control Enable      | $\rm X_0$ =0: Disable Internal Contrast Control(POR) $\rm X_0$ =1: Enable Internal Contrast Control Internal contrast circuits can be disabled if external contrast circuits is preferred.                                                                                                                                                        |

| 0011001X <sub>0</sub>                                           | Set Display Frequency                 | $X_0=0$ : Normal display frequency (POR)<br>$X_0=1$ : Half display frequency                                                                                                                                                                                                                                                                      |

| 0011010X <sub>0</sub>                                           | Save/Restore GDDRAM Column<br>Address | $X_0=0$ : Restore address $X_0=1$ : Save address                                                                                                                                                                                                                                                                                                  |

SOLOMON SSD1809 REV1.3 03/02

| Bit Pattern                                                     | Command                                | Comment                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|